在人工智能大模型爆发和全球算力需求呈指数级增长的今天,传统硅基芯片正面临“摩尔定律”的物理瓶颈。在“电”的传输速率和功耗渐显疲态之时,“光”以其超高速率、超大带宽和极低功耗的物理特性,正成为新一代算力网络的基石。而这颗跳动在数据中心、智能汽车与5G通信网络深处的“心脏”,正是光芯片。

如果说纵观“光芯片产业链全景”,上游的化合物半导体材料是物理基石,下游的AI、算力网络是应用汪洋,那么中游的光芯片制造,无疑是整条产业链的“价值核心”与技术高地。与传统硅基芯片的标准化CMOS工艺不同,光芯片的加工制造依赖于砷化镓(GaAs)、磷化铟(InP)等特殊的衬底材料,其外延生长、光刻刻蚀以及高精度封测过程,充满了极高的技术壁垒。

为了加强产业链上下游交流,艾邦建立有光通信产业链交流群,包括AI服务器,通讯设备,光芯片,光模块,光器件,零部件,光学元件,封装设备,材料,光模块连接器,高速铜缆,光纤等;欢迎大家识别下方二维码申请加入!

光芯片是以InP、GaAs、硅等半导体材料为衬底,通过微纳加工工艺制备,以光子为信息载体,完成光电信号转换、调制、传输与处理的核心器件。按功能可分为有源光芯片与无源光芯片两大类。

● 有源光芯片:负责实现光电转换,是高速光模块的核心

激光器芯片:

VCSEL(GaAs 系列):短距高速、3D 感知、数据中心短距互联

FP(InP 系列):中低速场景 DFB(InP 系列):25G/50G 主流方案

EML(InP 系列):800G/1.6T 超高速核心,行业刚需

探测器芯片(InP 系列):

APD:高灵敏、长距传输

PIN:中短距通用场景

调制器芯片(InP/LiNbO₃系列):光信号高速调制,超高速通信核心部件

● 无源光芯片:光路调控枢纽

无光电转换功能,基于 Si/SiO2 体系,核心品类包括 PLC、波分复用、光纤耦合器、光开关等,负责光信号的分配、耦合与切换,是光通信网络的基础支撑。

衬底材料直接决定光芯片上限,当前形成四条主流路线:

1、 磷化铟(InP)

高端主流,电子迁移率高、发光效率优,适配25G+高速长距场景,是800G/1.6T光模块、相干光模块核心方案,全球高端InP基芯片被海外垄断。

2、 砷化镓(GaAs)

中低端主力,成本低于InP,适配10G及以下场景、VCSEL芯片,国内企业已实现规模化自主。

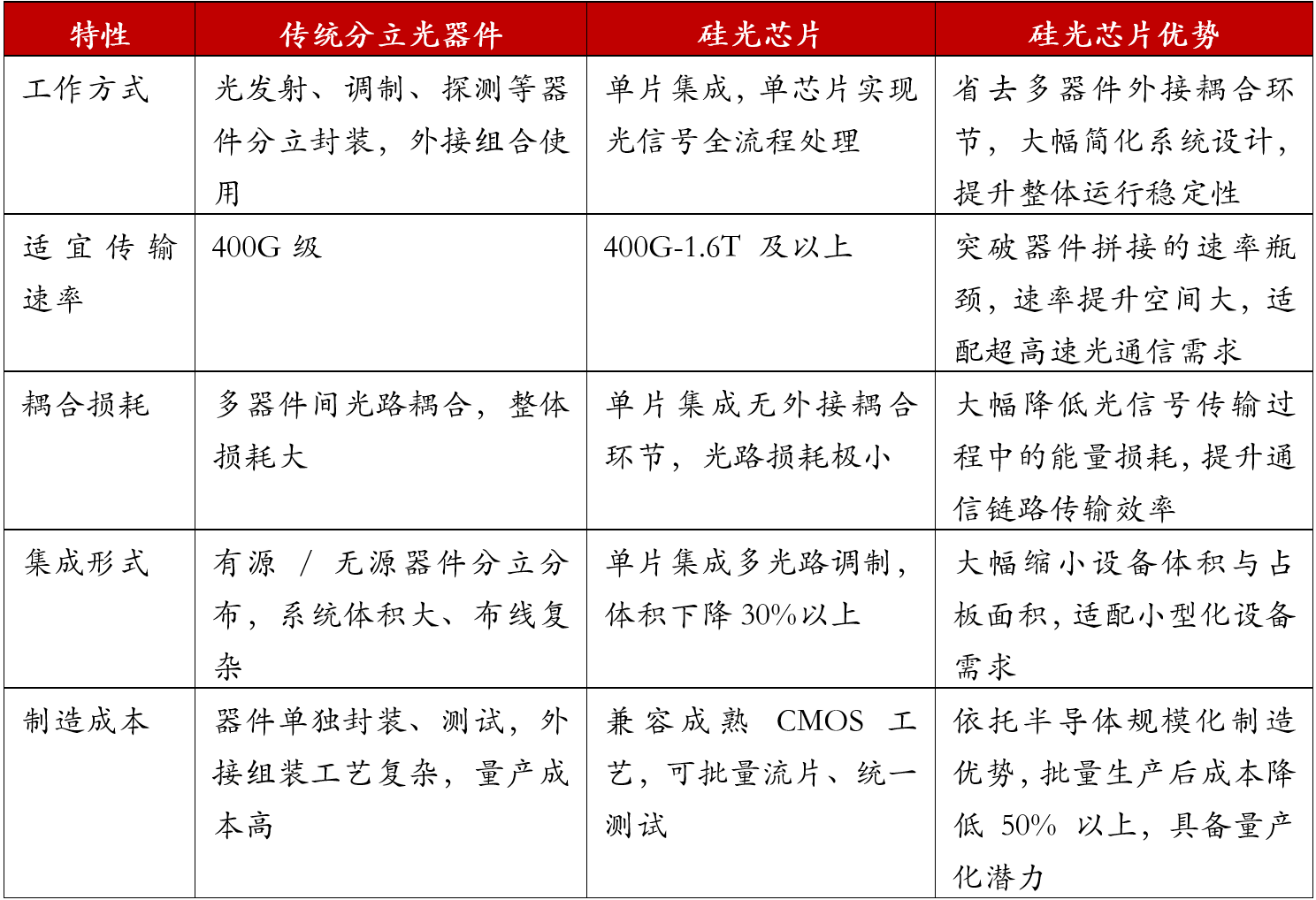

3、 硅光(Silicon Photonics)

下一代核心路线,依托CMOS工艺,成本降30%+、功耗降50%,800G及以上光模块、CPO共封装核心方案,2026年渗透率预计突破50%。

4、 薄膜铌酸锂(TFLN)

新兴高端路线,调制速率达100Gbps+,低损耗、高稳定,是3.2T+超高速光模块、下一代CPO核心技术,国内已实现技术突破,处于量产验证阶段。

光芯片的加工制造流程因材料和技术路线不同而有所差异,以下是常见光芯片(如硅基光芯片、磷化铟基光芯片)的典型加工制造流程:

硅基光芯片:采用绝缘衬底上的硅(SOI)晶圆,由硅衬底、埋氧层(二氧化硅)和顶层硅层组成。通过提纯、拉晶、切割、抛光等工序制备高纯度硅晶圆,确保表面平整度和晶格完整性。

磷化铟(InP)基光芯片:以磷化铟晶体为衬底,通过垂直梯度冻结法(VGF)或垂直舟式法(VB)等生长技术制备磷化铟晶锭,再切割、抛光成晶圆,需控制晶圆厚度、翘曲和位错密度。

磷化铟薄膜衬底,来源:精葳光学

我国在InP和GaAs衬底方面已基本具备进口替代的能力,根据Yole,国产厂商北京通美在2020年已成为全球InP衬底第二大供应商,市占率高达35%,仅次于住友电工;在2019年全球GaAs衬底市场中占据13%的市场份额,位居行业第三。

在衬底上通过金属有机化学气相沉积(MOCVD)或分子束外延(MBE)技术,生长具有特定光电性能的外延层。例如,在磷化铟衬底上生长铟镓砷磷(InGaAsP)等合金层,形成量子阱结构,以定义光芯片的发光波长、增益特性等关键参数。

-

按照外延生长材料的类型,外延可分为同质外延和异质外延。同质外延是指外延层与衬底材料相同的外延工艺,例如在Si衬底上外延Si,在GaAs衬底上外延GaAs等。这种外延方式能够充分利用衬底的特性,生长出与衬底晶格匹配良好的外延层,减少晶格缺陷,提高外延层的质量。异质外延则是外延层与衬底材料不同的外延工艺,如Si上外延SiGe,GaAs上外延GaAlAs等。异质外延为实现不同材料之间的优势互补提供了可能,通过合理选择外延层和衬底材料,可以获得具有特殊性能的半导体结构,满足不同器件的需求。

-

按照工艺划分,外延可分为气相外延(VPE)、液相外延(LPE)、固相外延(SPE)和分子束外延(MBE)等。不同的外延工艺具有各自的特点和适用范围,在半导体制造中发挥着不同的作用。

-

按照电阻率高低划分,外延可分为正向外延和反向外延。正向外延是在低阻衬底上外延高阻层(重衬底上外延生长轻掺杂层),而反向外延则是在高阻衬底上外延低阻层(轻掺杂衬底上外延生长重掺杂层)。这种分类方式主要是根据外延层和衬底的电阻率差异来进行的,不同的电阻率分布会对器件的性能产生重要影响。

-

按照压力划分,可分为常压外延(100kPa)和低压(减压)外延(5 - 20kPa)。压力对外延生长过程中的气体传输、化学反应以及薄膜质量等方面都有着显著的影响,选择合适的压力条件能够优化外延工艺,提高外延层的质量和均匀性。

-

按照温度划分,可分为反应温度在1000℃以上的高温外延和1000℃以下的低温外延。温度是外延生长过程中的一个关键参数,它直接影响着化学反应速率、原子扩散速率以及外延层的晶体结构和质量。不同的外延工艺和材料对温度的要求各不相同,需要根据具体情况进行精确控制。

外延生长需精确控制温度、压力、气体流量等参数,确保外延层厚度、成分和掺杂均匀性,这是光芯片制造中技术壁垒最高的环节。

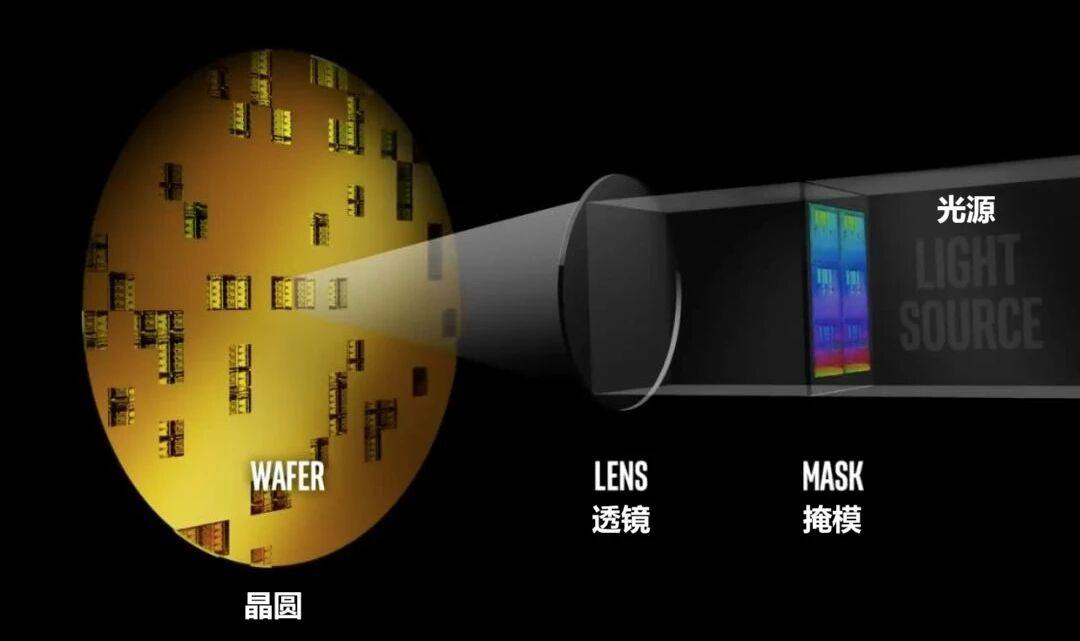

光刻:利用光刻技术将芯片设计图案转移到外延片上,定义光波导、光栅、电极等结构。

光刻

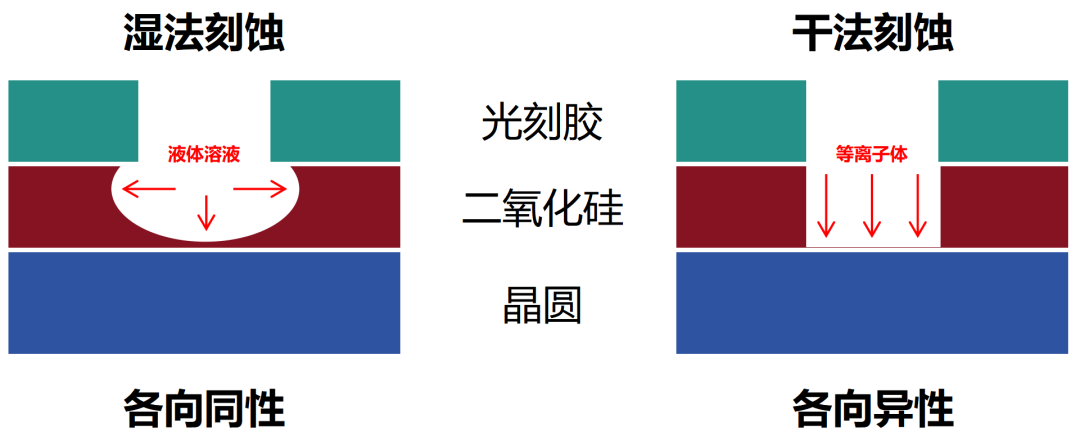

刻蚀:通过干法刻蚀或湿法刻蚀,去除多余材料,形成所需的三维结构,如波导通道、光栅齿等。

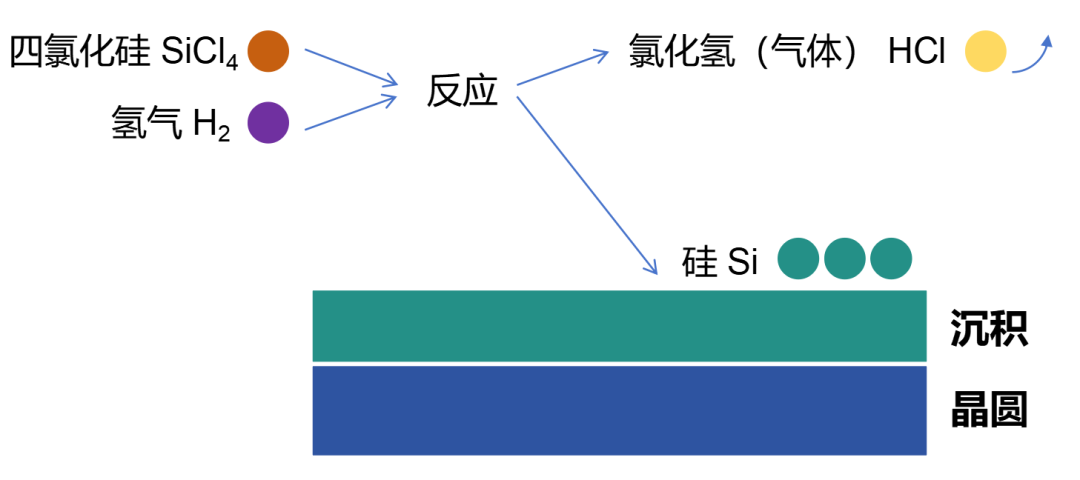

薄膜沉积与金属化:沉积绝缘层、导电层等薄膜,并通过金属化工艺形成电极和互连结构,实现芯片的电学功能。

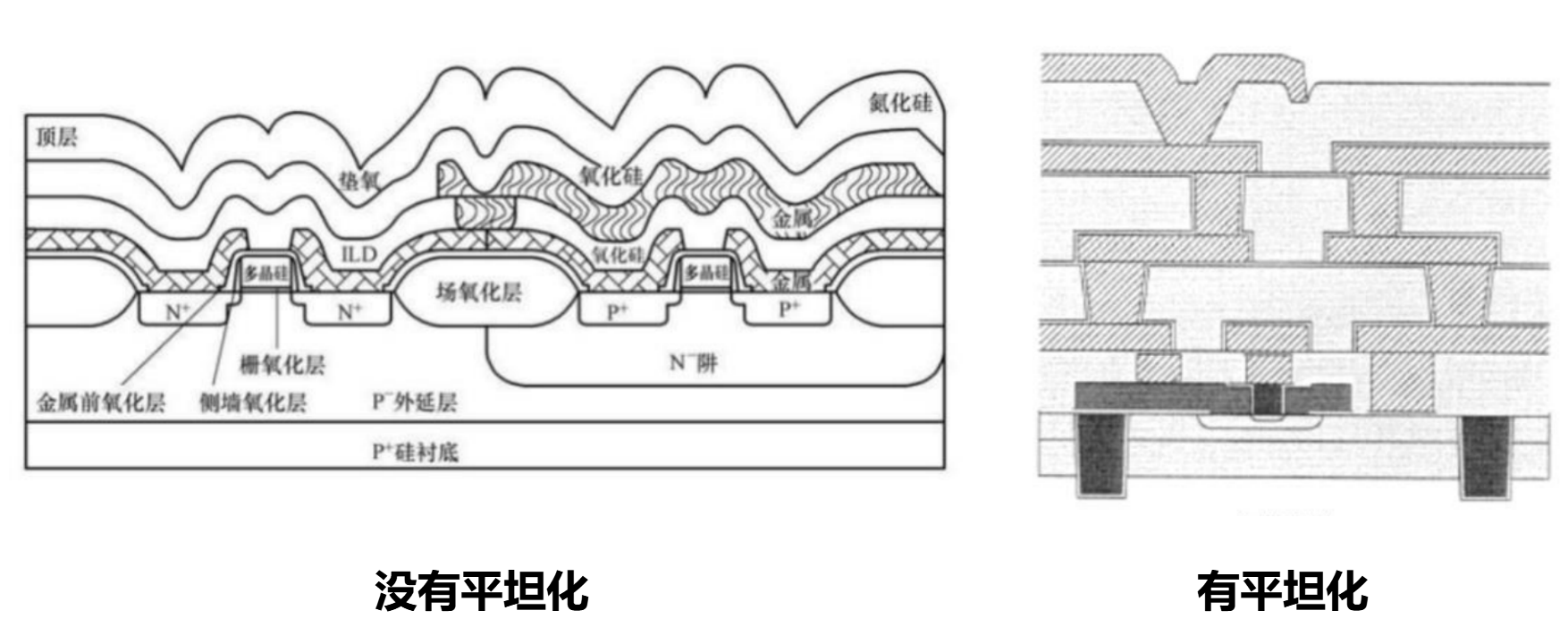

平坦化:采用化学机械抛光(CMP)等技术,使晶圆表面平整,便于后续工艺操作。

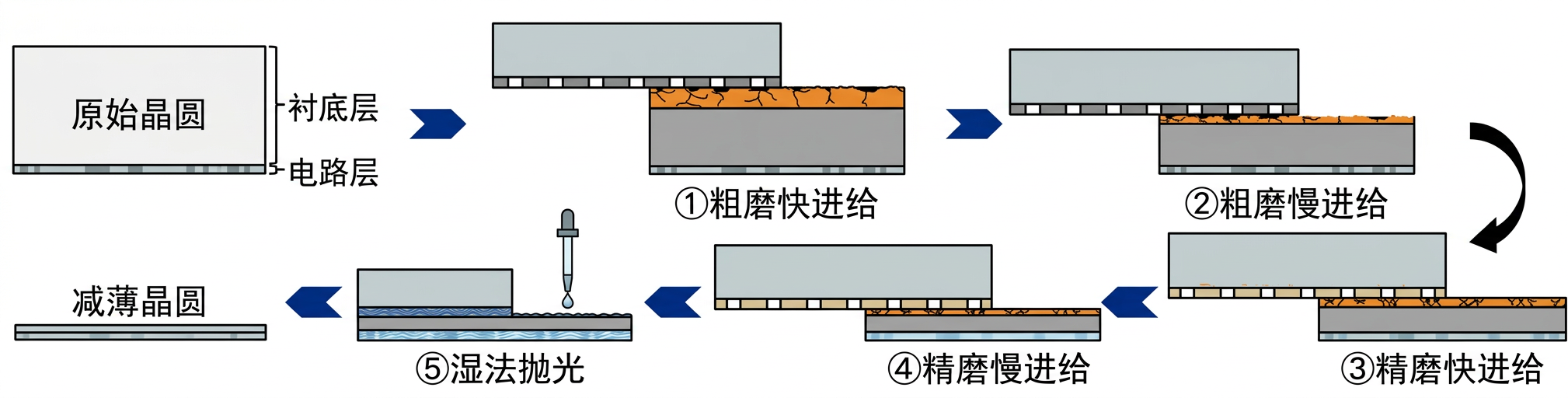

减薄:对晶圆进行背面研磨或化学机械抛光,降低厚度,便于后续切割和封装。

解理:将晶圆切割成单个芯片,形成可独立使用的光芯片裸片。

在芯片端面沉积抗反射膜或高反射膜,优化光信号的发射和接收效率,减少光损耗。

电学测试:检测芯片的电气性能,如电流-电压特性、阈值电流、斜率效率等。

光学测试:通过光谱分析、光功率测量、调制响应测试等,评估芯片的光学性能,筛选出合格芯片。

芯片贴装:将芯片固定在封装基板或外壳上,通过焊料、胶粘剂等方式实现机械和电气连接。

光耦合:采用主动对准或被动对准技术,将芯片与透镜、光纤等光学元件精确耦合,确保光信号的高效传输。

密封与保护:对封装体进行气密性密封,防止湿气、灰尘等污染物进入,保护芯片性能。

对封装后的光芯片进行高温老化、温度循环、振动测试等可靠性测试,验证芯片在长期运行条件下的性能和稳定性,确保符合应用要求。

不同类型的光芯片(如硅光芯片、VCSEL芯片等)在具体工艺细节上可能有所差异,但整体流程均围绕衬底制备、外延生长、晶圆制造、封装测试等核心环节展开。

为了加强产业链上下游交流,艾邦建立有光通信产业链交流群,包括AI服务器,通讯设备,光芯片,光模块,光器件,零部件,光学元件,封装设备,材料,光模块连接器,高速铜缆,光纤等;欢迎大家识别下方二维码申请加入!

视频资讯:

推荐活动:2026年第三届 AI算力服务器液冷技术产业发展论坛

微信扫描下方的二维码阅读本文